标签:

摘要: 当半导体业界在夸耀新制程技术突破、摩尔定律持续适用时,对封装技术者来说,苦头才正要开始,因为用新制程实现的芯片不可能以裸晶方式来运作,一定要有对应、搭配新制程的芯片封装,然而制程技术愈是先进、缩密,封装技术就要承受愈多新制程所一并带来的压力与挑战,要因应新压力与新挑战,也就意味著封装技术要有新作法、新尝试,才能克服或舒缓新压力。封装也可以说是指安装半导体集成电路芯片用的外壳,它不仅担任放置、固定、

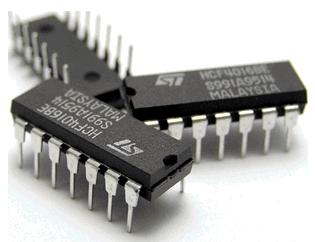

早期DIP封装

芯片的封装技术种类实在是多种多样,诸如DIP,PQFP, TSOP, TSSOP, PGA, BGA, QFP, TQFP, QSOP, SOIC, SOJ, PLCC, WAFERS……一系列名称,看上去都十分繁杂,其实,只要弄清芯片封装发展的历程也就不难理解了。

芯片的封装技术已经历经好几代的变迁,技术层级一代比一代先进,包括芯片面积与封装面积之比越来越接近,适用频率越来越高,耐热性能越来越好,以及导线数增多,导线间距减小,重量减小,可靠性提升,使用更加方便等等,都是看得见的变化。

20世纪70年代时,芯片封装流行的还是对称脚位封装,简称DIP(Dual ln-line Package)。DIP封装在当时具有适于在PCB的导孔上焊接固定的特性,具有比TO型封装易于对PCB布线以及操作较为方便等一些特点,其封装的架构形式也很多,包括多层陶瓷DIP,单层陶瓷DIP,导线框架式DIP等等。但是衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。比如一颗采用40根I / O导线塑料双列直插式封装(PDIP)的芯片为例,其芯片面积/封装面积=(3 x3)/(15.24 x 50)=1︰86,离1相差很远。不难看出,这种封装尺寸远比芯片大的多,说明封装效率很低,占去了很多有效安装面积。

20世纪90年代随著合成技术的进步、设备的改进和新制程的使用,LSI、VLSI、ULSI相继出现,芯片合成度不断提升,I / O导线数急剧增加,功率也随之增大,对集成电路封装的要求也更加严格。

▲大众对集成电路、IC、芯片的第一印象,即是过往最普及盛行的DIP封装模样,长条、穿孔焊接用的金属接脚,使整个封装的外型容易与蜈蚣联想在一起,DIP封装小至4-pin、6-pin,大至40-pin、68-pin。然今日已愈来愈少使用。

近代球式封装--BGA

BGA封装为何能够容纳更多的接脚数?答案在于:再次改变接脚配置、设计的规则,过去DIP仅用封装的左右侧边,QFP则是使用四个侧边,如此接脚数目的增加都受限在边长上,要增加边长就必须增加封装体的长宽面积,进而使封装成本增加。相对的,BGA运用整个封装体的底部面积来安排、设置接脚,接脚的放置从「四个侧边」改成「整个底面」,如此自然可以让接脚数目大增。为满足发展的需要,在原有封装模式的基础上,又增添了新的模式──球格式封装(Ball Grid Array,BGA,也称为锡球阵列封装或锡脚封装体)。

BGA 封装技术有这样一些特点︰I / O导线数虽然增多,但导线间距并不小,因而提升了组装良率;虽然它的功率增加,但BGA能改善它的电热性能;浓度和重量都较以前的封装技术有所减少,信号传输延迟小,使用频率大大提升,可靠性高。不过BGA封装仍然存在著占用基板面积较大的问题。

▲美国美光(Micron)公司的RLDRAM(RL为Reduced Latency,延迟缩减之意)存储器,单颗容量576Mbits,采行144-pin BGA封装,图中可见BGA封装的接脚为「锡球」状。

渐露头角的CSP

在BGA技术开始推展的同时,另外一种从BGA发展来的CSP封装技术正在逐渐展现它生力军本色。

CSP,全称为Chip Scale Package,即芯片型封装的意思,也有人称Chip Size Package,相同的缩写字母(S)却有不同的全写字。作为新一代的芯片封装技术,在BGA、TSOP的基础上,CSP的性能又有了大量的跃升。

CSP封装可以让芯片面积与封装面积约为普通的BGA的1/3,仅仅相当于TSOP存储器芯片面积的1/6。这样在相同体积下,集成电路可以装入更多的芯片,从而增大单位容量。也就是说,与BGA封装相比,同等空间下CSP封装可以将储存容量提升三倍。不过,也有人直接以面积来定义,只要外部封装面积小于内部裸晶面积的150%,都能算是CSP。CSP封装不但体积小,同时也更薄,其金属基板到散热体的最有效散热路径仅有0.2mm,大大提升了芯片在长时间运作后的可靠性,线路阻抗显著减小,芯片速度也随之得到大幅度的提升。

此外,环保上的压力,芯片(或封装)业者近年来就已经感受到压力,因此提出了无铅式封装(Lead Free),有的强调全公司的芯片产品都已奉行无铅政策,有的是9x%以上的产品都已采行无铅,另外也有自我发布承诺,在200x年以后会迈入完全无铅出货。这些环保法律限令也一样要考验现有的封装技术与制程。

上一篇:3G智能手机视频监控分析

| 型号 | 厂商 | 价格 |

|---|---|---|

| EPCOS | 爱普科斯 | / |

| STM32F103RCT6 | ST | ¥461.23 |

| STM32F103C8T6 | ST | ¥84 |

| STM32F103VET6 | ST | ¥426.57 |

| STM32F103RET6 | ST | ¥780.82 |

| STM8S003F3P6 | ST | ¥10.62 |

| STM32F103VCT6 | ST | ¥275.84 |

| STM32F103CBT6 | ST | ¥130.66 |

| STM32F030C8T6 | ST | ¥18.11 |

| N76E003AT20 | NUVOTON | ¥9.67 |