标签:

摘要: 摘要:实现了一种全集成可变带宽中频宽带低通滤波器,讨论分析了跨导放大器-电容(OTA—C)连续时间型滤波器的结构、设计和具体实现,使用外部可编程电路对所设计滤波器带宽进行控制,并利用ADS软件进行电路设计和仿真验证。仿真结果表明,该滤波器带宽的可调范围为1~26 MHz,阻带抑制率大于35 dB,带内波纹小于0.5 dB,采用1.8 V电源,TSMC 0.18μm CMOS工艺库仿真,功耗小于21 mW,频响曲线接近理想状态。关键词:Butte

在便携式数字卫星通信系统中,为了扩大传输容量和提高传输效率,满足同时传输几种业务的需求,通常采用时分复用的方法,将若干个低速数字码流按一定格式合并成一个高速数据码流,以便在一条信道中传输,使各个业务信号互相不产生干扰,实现此功能的设备就是数字复接系统。

便携式卫星通信,要求实现平台集成度高、速度快、功耗小、体积小和成本低。现场可编程门阵列(FPGA) 在结构上由逻辑功能块排列为阵列,并由可编程的内部连线连接这些功能块,来实现一定的逻辑功能。特别适合上述要求的产品开发与小批量生产。

FPGA 的开发环境在电路设计阶段,可实时地对设计电路进行各种仿真分析,提高电路设计的灵活性和可靠性,特别是还可在成品上直接进行二次开发和功能扩展,灵活且可移植。后期还可以在线对任意一逻辑信号进行实时仿真,该文利用软件Quartus II 5. 1 和VHDL 硬件语言进行设计和仿真,实现一个基于FPGA 的卫星便携站的同步数字复接系统的设计。

1 设计和实现

同步数字复分接器完成以下业务的复分接:3 路音频合计48 kbps 数据; 1 路64 kbps 同步数据;1 路9. 6 kbps 异步数据; 1 路128 kbps LAN 数据; 1 路517. 2 kbps 视频数据。采用同步、固定时隙分配和按位复接方式的设计方法。

1.1 准同步时延

因为数字复接器与音频的接口关系最为复杂,所以设计要点着重放到了与音频接口的处理。

1. 1. 1 音频接口的乒乓操作

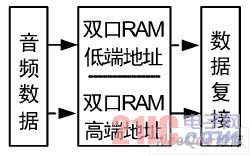

如图1 所示,采用双口RAM 完成音频数据和复分接器的接口。音频数据接口是一种DSP 总线接口,在第1 个缓冲周期,音频数据缓存到双口RAM的低端地址存储区,同时数据复接单元读取双口RAM 的高端地址存储区的音频数据; 在第2 个缓冲周期,音频数据缓存到双口RAM 的高端地址存储区,同时数据复接单元读取双口RAM 的低端地址存储区的音频数据。如此循环,周而复始。

图1 乒乓操作示意图

这样经过缓冲的数据流没有时间停顿的送到复接器中,属于一种流水线式处理,完成数据的无缝缓冲和处理,节约缓冲区的空间,达到利用低速模块处理高速数据流的结果,实现了数据流的并串转换。

如果音频数据和复分接器的接口采用传统的缓存方式,很容易造成复接器读数据的时候音频数据还没有写到缓存中,很容易造成声音的“咔咔声”,采用音频接口的乒乓操作避免了此问题的产生。

1. 1. 2 提供唇音同步机制

在数字卫星传输系统中,有一个独特的音视频同步问题,即通常说的唇音同步。由于图像压缩编码所需之信号处理时间一般慢于声音压缩编码所需之信号处理时间,那么在收端将视频及音频信号解码出来后,就会发现音频比视频快半拍。通常见到的情况是,或者口动时听不到声音,或者口不动时却有声音出来,即唇音不同步,给观众较差的主观感觉。为了避免出现这一问题,分接器中提供了唇音同步单元,把音频数据程序上进行延时,通过调整就可保证接收端的音和视频同步。

1. 1. 3 解决FPGA 电路设计中的毛刺问题

在FPGA 中当多路信号同时发生跳变的瞬间,往往会出现一些不正确的尖峰信号,这些尖峰信号就是“毛刺”。组合逻辑电路中竞争冒险现象的出现也会出现“毛刺”。它的出现会影响电路工作的稳定性和可靠性,导致数字系统的误操作和逻辑紊乱。

设计中利用D 触发器对输入信号的毛刺不敏感的特点,去除信号中的毛刺,但是只是对信号中发生在非时钟跳变沿的毛刺信号去除明显,并且有一定延时。因此设计中尽量采用同步时序电路来实现各个进程模块的功能,同时对输入输出的数据进行高倍时钟的采样,达到去除电路中毛刺的目的。

上一篇:自动显微镜调焦原理

| 型号 | 厂商 | 价格 |

|---|---|---|

| EPCOS | 爱普科斯 | / |

| STM32F103RCT6 | ST | ¥461.23 |

| STM32F103C8T6 | ST | ¥84 |

| STM32F103VET6 | ST | ¥426.57 |

| STM32F103RET6 | ST | ¥780.82 |

| STM8S003F3P6 | ST | ¥10.62 |

| STM32F103VCT6 | ST | ¥275.84 |

| STM32F103CBT6 | ST | ¥130.66 |

| STM32F030C8T6 | ST | ¥18.11 |

| N76E003AT20 | NUVOTON | ¥9.67 |